89c52 35i pdip40 что это такое

Русские Блоги

51 однокристальный микрокомпьютер STC89C52RC усовершенствованная 51-однокристальная минимальная система на макете

Подготовка электронного компонента

Микросхема STC 89C52RC (40-контактный DIP-пакет) x 1

Алюминиевый электролитический конденсатор 10 мкФ х 1

Встроенное сопротивление 10К х 2

11.0592 МГц кварцевый генератор x 1

Керамический конденсатор 30 пФ х 2

Значок электронных компонентов

Осмотрите сторону и посмотрите на корпус конденсатора в продольном направлении. Сторона, отмеченная символом «-», следует за трендом, вывод в этом направлении отрицательный, а противоположный вывод положительный.

STC 89C52RC электрические характеристики

Определение булавки

| Символ булавки | Пин код | Пин-смысл | замечания |

|---|---|---|---|

| T2/P1.0 8 | 8-битный двунаправленный порт ввода-вывода с внутренним подтягивающим резистором | Данные можно вводить или выводить. В то же время он может использоваться как вход внешней технологии (P1.0 / T2) и триггерный вход (P1.1 / T2EX) таймера / счетчика 2. | |

| RST | 9 | Сбросить ввод | Используется для завершения операции инициализации сброса микроконтроллера |

| RXD/P3.0 | 10 | Последовательный ввод | При использовании загрузчика USB-TTL для записи программ этот интерфейс обычно подключается к выводу TXD загрузчика. |

| TXD/P3.1 | 11 | Последовательный порт | При использовании загрузчика USB to TTL для записи программ этот интерфейс обычно подключается к выводу RXD загрузчика. |

| INTO/P3.2 | 12 | Порт внешнего прерывания 0 | |

| INT1/P3.3 | 13 | Порт внешнего прерывания 1 | |

| TO/P3.4 | 14 | Таймер 0, внешний вход | |

| T1/P3.5 | 15 | Таймер 1, внешний вход | |

| WR/P3.6 | 16 | Внешняя память данных записывает строб | |

| RD/P3.7 | 17 | Внешняя память чтения данных строб | |

| XTAL2 | 18 | Входная клемма генератора инвертирующего усилителя | |

| XTAL1 | 19 | Входной вывод генератора, инвертирующего усилитель и внутреннюю тактовую генераторную цепь | |

| VSS | 20 | Наземный (GND) терминал | |

| P2.0/A8 28 | 8-битный двунаправленный порт ввода-вывода с внутренним подтягивающим резистором | Данные могут быть введены или выведены | |

| PSEN | 29 | Внешний ROM считывает строб-сигнал | При доступе к памяти вне кристалла этот терминал выводит отрицательный импульс в качестве стробирующего сигнала чтения памяти |

| ALE/PROG | 30 | Защелка адреса позволяет / на кристалле программировать импульс EPROM | ALE: используется для фиксации низкого 8-битного адреса, отправленного с порта P0. PROG: микросхема с микросхемой EPROM. Во время программирования EPROM этот вывод вводит импульсы программирования |

| EA | 31 | Доступ к внешнему сигналу управления памятью программы | Для выполнения внутренних программных инструкций он должен быть подключен к положительному источнику питания. |

| P0.0/AD0 39 | 8-битный двунаправленный порт ввода-вывода с открытым стоком | Данные могут быть введены или выведены | |

| VCC | 40 | Мощность положительного входа | Подключите источник питания положительным |

Таким образом, используя STC 89C52RC для построения 51 минимальных системных схем, STC

Контакты 89C52RC должны быть подключены в 6 местах. «Символы выводов» 6 подключаемых выводов отмечены красным шрифтом, а порядок их подключения поясняется комментариями.

Дополнение: Примечания к таблице:

Принципиальная электрическая схема

Это минимальная принципиальная схема системы, описанная в официальном документе.

Это дополнительная краткая принципиальная схема системы с кратким указанием версии 51 в высоком разрешении.

Построение минимальной схемы системы

Согласно «Минимальной системе STC 89C52RC»

принципиальная схема «, вставьте все оригиналы в макет.

Как показано на рисунке после вставки:

На рисунке ниже показан новый метод построения, который был улучшен позже. Это яснее, чем раньше, и углы сделаны так, чтобы углы могли освободить место для пересечения и облегчить наблюдение и понимание.

Программирование

Чтобы записать программу, вам нужно использовать USB для TTL. Добавьте наименьшую системную схему.

Модернизация цепи

Оригинальная схема должна быть подключена к загрузчику программы USB to TTL, чтобы записать программу. Поскольку загрузчик с USB на TTL имеет выходную мощность 5 В, он также работает как источник питания без записи программы.

Ключевым моментом программного загрузчика USB-TTL является то, что контакты TXD и RXD загрузчика должны быть подключены к контактам TXD и RXD микросхемы наоборот.

В загрузчике с USB на TTL необходимо подключить только 4 контакта, а 3,3 В не нужно подключать.

Установка и настройка программной среды

перед началом

Среда и программное обеспечение, необходимые для программирования 51 однокристального микрокомпьютера, являются следующими:

Драйвер загрузчика USB to TTL (здесь загрузчик USB to TTL чипа CH340)

Keil for C51 IDE(Version 4)

Чтобы установить драйвер загрузчика под Win10, вы должны запустить его с отключенным драйвером подписи перед установкой

Не загружайте Keil IDE в версию ARM, нет связанной с CPU опции C51

Установить драйвер USB на TTL

Baidu поиск драйвера CH340, скачать и установить

Установите Keil IDE

Baidu поиск «keilc51», скачать и установить. Внутри обычно есть учебники по взлому, просто следуйте инструкциям. Обратите внимание, что версия является лучшей версией

4。

Установить STC-ISP

Поиск Baidu «STC-ISP», скачать и установить. Это программное обеспечение не требует установки и может быть запущено двойным щелчком после загрузки и распаковки.

Используйте Keil, чтобы написать программу, чтобы зажечь светодиод

Появится диалоговое окно «Выберите тип устройства ЦП», и в дереве слева выберите «Atmel» по очереди.

«AT89C52», нажмите «ОК».

На вкладке «Проект» слева найдите «Исходная группа 1», щелкните правой кнопкой мыши «Добавить файлы в

Group‘Source Group

1 ’», выберите файл языка c с только что сохраненным суффиксом c, нажмите «Добавить» и закройте диалоговое окно.

Напишите следующий код в файле языка c:

После сохранения щелкните следующий значок, чтобы установить выходной шестнадцатеричный файл:

Во всплывающем диалоговом окне перейдите на вкладку «Вывод» и установите флажок «Создать HEX».

File «, оставьте значение по умолчанию, просто нажмите» OK «.

После сохранения щелкните следующий значок, чтобы начать компиляцию:

Выше указано, что компиляция прошла успешно. Файл с шестнадцатеричным суффиксом будет создан в том же каталоге проекта.

Используйте программу STC-ISP для записи программы

В это время убедитесь, что драйвер USB-TTL установлен, а загрузчик USB-TTL вставлен в порт USB компьютера.

После вставки загрузчика система автоматически обнаружит USB-устройство, и в «Порт» в «Диспетчере устройств» появится COM-порт, соответствующий этому устройству.

Откройте программное обеспечение STC-ISP, сначала выберите «Модель однокристального микрокомпьютера». Здесь выберите «STC89C52RC».

Проверьте, обнаружен ли COM-порт загрузчика по «Серийному номеру».

Выше приведено успешное обнаружение загрузчика.

Нажмите «Открыть файл программы» и выберите только что созданный шестнадцатеричный файл.

Нажмите «Скачать / Программа»:

В это время сначала отключите шнур питания 5 В USB-загрузчика TTL, а затем снова подключите его, чтобы запустить холодный запуск, и снова проследите за подтверждением связи, чтобы программа начала мигать.

Вывод результатов в поле вывода журнала программного обеспечения:

Вышеуказанное означает, что программа успешно запрограммирована, и программа будет выполнена немедленно.

расширять

После того, как программа была сожжена, программа будет выполняться постоянно, пока источник питания всегда подается. Но я не хочу подключать загрузчик все время, это слишком громоздко. Позже я использовал кабель для передачи данных мобильного телефона (должен быть 4-ядерным, я не знал, какое устройство я обнаружил в начале, но он был 2-ядерным). После зачистки подключите красный провод к положительному входу блока питания и черный провод к GND. Линия USB может быть подключена к любому порту USB, а микрокомпьютер с 51 микросхемой работает нормально.

Код переключателя светодиода ВКЛ / ВЫКЛ с интервалом в 1 секунду:

89c52 35i pdip40 что это такое

Эта серия имеет минимальные отличия от оригинальной архитектуры MCS51. Цоколевка корпусов совпадает со старыми микроконтроллерами 8031, 8051, 8052, 8058, I8751, AT89C51, и т. п., что облегчает апгрейд существующих готовых систем. Т. е. можно вынуть из системы старый микроконтроллер и заменить его на новый, получив дополнительные возможности и двукратное повышение производительности, иногда при этом даже не потребуется перекомпилировать исходное программное обеспечение.

Серия STC89xx представляет 8-битные микроконтроллеры, которое полностью совместимы по системе команд с индустриальным стандартом серии микроконтроллеров 80C51. Имеется 64K байт памяти flash для программы приложения, которая может программироваться в рабочей системе (In-System-Programming, ISP). Есть также возможность самопрограммирования из программы пользователя (In-Application-Programming, IAP). ISP позволяет пользователям обновлять программу и данные, не извлекая микроконтроллер из системы. IAP по сути позволяет выполнять то же самое, но эта технология осуществляет перезапись памяти кода и/или данных, когда приложение выполняется в системе. Для приложения предоставляется 1280 или 512 байт встроенной в кристалл памяти RAM, что достаточно для многих встраиваемых приложений. Пользователь может конфигурировать микроконтроллер (MCU), запуская программу в режиме 12 тактов на 1 машинный цикл, получая при этом ту же самую низкоуровневую аппаратную архитектуру тактирования, как и оригинального устройства 80C51 других вендоров, либо можно сконфигурировать тактирования на 6 тактов на один машинный цикл, удваивая тем самым производительность ядра. Серия STC89xx сохраняет все аппаратные возможности стандартного устройства 80C51. Дополнительно имеется в распоряжении дополнительный порт ввода/вывода (P4), Timer 2, 8 источников прерывания с 4 уровнями приоритета, встроенный в кристалл генератор, и однократно разрешаемый сторожевой таймер (Watchdog Timer).

Список возможностей серии STC89xx:

[Внутренняя организация]

Ядро CPU серии STC89xx полностью совместимо со стандартным микроконтроллером 8051, с поддержкой всех мнемоник инструкций и сохранением совместимости по двоичному коду. Серия STC89xx может выполнять код в 2 раза быстрее, чем стандартный 8051 (режим тактирования 6T) или с обычной скоростью (режим тактирования 12T). Улучшение производительности отдельных программ зависит от реально используемых инструкций.

Рис. 1. Блок-диаграмма STC89xx.

[Таблица выбора микроконтроллеров STC89xx по общим параметрам]

| Тип | VCC, V | FLASH, байт | SRAM, байт | TIMER | UART | DPTR | EEPROM, байт |

| STC89C51RC | 3.3-5.5 | 4K | 512 | 3 | 1 | 2 | 4K |

| STC89C52RC | 3.3-5.5 | 8K | 512 | 3 | 1 | 2 | 4K |

| STC89C53RC | 3.3-5.5 | 13K | 512 | 3 | 1 | 2 | / |

| STC89LE51RC | 2.0-3.6 | 4K | 512 | 3 | 1 | 2 | 4K |

| STC89LE52RC | 2.0-3.6 | 8K | 512 | 3 | 1 | 2 | 4K |

| STC89LE53RC | 2.0-3.6 | 13K | 512 | 3 | 1 | 2 | / |

| STC89C54RD+ | 3.3-5.5 | 16K | 1280 | 3 | 1 | 2 | 45K |

| STC89C58RD+ | 3.3-5.5 | 32K | 1280 | 3 | 1 | 2 | 29K |

| STC89C516RD+ | 3.3-5.5 | 61K | 1280 | 3 | 1 | 2 | / |

| STC89LE54RD+ | 2.0-3.6 | 16K | 1280 | 3 | 1 | 2 | 45K |

| STC89LE58RD+ | 2.0-3.6 | 32K | 1280 | 3 | 1 | 2 | 29K |

| STC89LE516RD+ | 2.0-3.6 | 61K | 1280 | 3 | 1 | 2 | / |

У всех перечисленных в таблице моделей имеется прерывание по снижению VCC ниже допустимого уровня (INT Low VCC), 4 аппаратных внешних прерывания могут выводить MCU из режима сна (power down mode), сторожевой таймер (WDT).

Дополнительные аппаратные функции, которые не реализованы: PCA, PWM, D/A, ADC, настройка нижнего предела срабатывания прерывания порога допустимого напряжения питания, специальный таймер для пробуждения.

[Цоколевка, описание выводов]

|  |  |

[Размеры корпусов]

Микроконтроллеры серии STC89xx (STC89Cxx, STC89LExx) выпускаются в стандартных корпусах PQFP-44, LQFP-44, PDIP-40, PLCC-44, сохраняя цоколевку традиционных микроконтроллеров семейства MCS51. Размеры корпусов см. в даташите STC89C51RC-en.pdf [2].

[Управление питанием, сброс]

Всего есть 3 режима, в которых может находиться микроконтроллер: нормальный режим, режим ожидания (Idle mode) и режим выключения (Power-down mode). По умолчанию активен нормальный режим, в остальные режимы возможен вход с помощью программирования бит PD и IDL регистра PCON.

PCON (адрес 87h)

| Бит | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Имя | SMOD | SMOD0 | — | POF | GF1 | GF0 | PD | IDL |

PD : Power-Down bit, бит выключения. Установка этого бита поместит STC90C51RC/RD+ MCU в режим Stop/Power-Down, из которого можно вывести/разбудить MCU внешним прерыванием или сбросом. Из-за того, что в режиме Stop/Power-Down останавливают свою работу внутренний генератор, CPU, таймеры, UART и другие аппаратные блоки, то будет работать только блок внешнего прерывания. Следующие ножки могут разбудить MCU из Stop/Power-Down mode: INT0/P3.2, INT1/P3.3, INT2/P4.3, INT3/P4.2.

Ниже подробнее описан каждый из режимов пониженного энергопотребления.

Idle Mode (режим ожидания). Инструкция, которая установит бит IDL (PCON.0) приведет к тому, что она будет последней, которая была выполнена перед входом в idle mode. В этом режиме внутреннее тактирование отключается от ядра CPU, но не от функций блока прерываний, таймеров, WDT и последовательного порта. Статус CPU полностью сохраняет свое состояние: указатель стека (Stack Pointer, SP), счетчик инструкций (Program Counter, PC), слово состояния (Program Status Word, PSW), аккумулятор (Accumulator, A) и другие регистры будут хранить свои данные во время режима ожидания. Ножки портов будут удерживать свое логическое состояние, какое они имели в момент активации режима ожидания. На ножках ALE и PSEN удерживается лог. 1. Idle mode оставляет периферийные устройства работать, так что они могут разбудить CPU, когда генерируется прерывание. Timer 0, Timer 1, Timer 2 и UART будут продолжать свою работу в режиме ожидания.

Есть два способа прервать режим ожидания. Во-первых, активация любого разрешенного прерывания приведет к тому, что будет аппаратно очищен бит IDL, завершая тем самым действие idle mode. Прерывание будет обработано, и инструкция RETI на выходе из ISR продолжит выполнение программы со следующей инструкции, находящейся после инструкции, которая ввела микроконтроллер в режим ожидания.

Биты флагов (GFO и GF1) могут использоваться, чтобы искусственно показать, было ли прерывание сгенерировано во время обычной работы или во время режима ожидания. Например, если инструкция, активирующая idle mode, установила один или оба этих флага вместе с битом IDL (операцией OR над регистром PCON). Тогда если выход из idle mode был осуществлен прерыванием, то прерывание может заметить этот факт, анализируя содержимое флагов GF0 и GF1.

Во-вторых, пробуждение процессора будет вызвано подтягиванием ножки сброса RESET к лог. 1, вызывая генерацию внутреннего аппаратного сброса. Поскольку тактовый генератор все еще работает, аппаратный сброс должен удерживаться в активном состоянии только на 2 системных тактовых цикла (24 такта системной частоты), чтобы сброс был завершен.

Power Down (PD) Mode. Инструкция, которая установит бит PD (PCON.1), приведет к тому, что это будет последняя выполненная инструкция перед входом в режим выключения (Power-Down mode). В Power-Down mode, будут выключены встроенный генератор и память FLASH, чтобы минимизировать потребление энергии. В этом режиме потреблять ток будет только схема включения (power-on circuit). Содержимое встроенной памяти RAM и регистров специального назначения (Special Finction Register, SFR) сохраняется.

Примеры кода, демонстрирующие выход из power-down mode по внешнему прерыванию на языках C и ассемблера см. в даташите STC89C51RC-en.pdf [2].

Управление сбросом, работа вывода RESET, сброс по включению питания (Power-On Reset, POR), программный сброс, описание встроенного супервизора MAX810, описание регистра PCON, описание работы сторожевого таймера (Watch-Dog-Timer, WDT), пример кода с WDT, см. в даташите STC89C51RC-en.pdf [2].

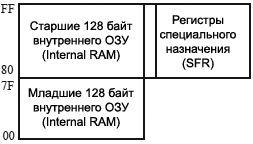

[Организация памяти]

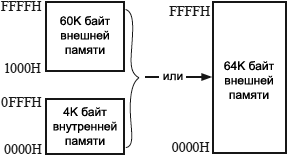

Микроконтроллер (далее сокращенно MCU) серии STC89xx имеют раздельные адресные пространства для памяти программ (Program Memory) и памяти данных (Data Memory), это так называемая Гарвардская архитектура (см. Википедию).

После сброса CPU начинает выполнение кода с адреса 0000H Program Memory, где должен начинаться код приложения пользователя. Для обработки прерываний код ISR должен размещаться в памяти программ по специальным адресам, которые называют векторами прерываний. Каждому прерыванию назначен фиксированный адрес вектора в памяти программ. Когда происходит прерывание, то CPU переходит к выполнению кода по вектору прерывания, приостанавливая выполнение основной программы (или менее приоритетного прерывания). Например, вектор External Interrupt 0 назначен на адрес 0003H. Если используется External Interrupt 0, то его ISR должен начинаться с адреса 0003H (обычно в этом месте находится команда безусловного перехода AJMP или LJMP). Если прерывание не используется, то место под код его вектора свободна как обычная память программ.

Ячейки векторов прерываний идут друг за другом с интервалом 8 байт: 0003H вектор для External Interrupt 0, 000BH для прерывания Timer 0, 0013H для External Interrupt 1, 001BH для Timer 1, и т. д. Если ISR достаточно короткий, то он может уложиться в этом 8-байтном интервале. Более длинные ISR могут использовать инструкцию перехода (AJMP или LJMP) для пропуска следующих на ней ячеек других векторов прерываний, если эти прерывания используются.

Ниже показано для примера распределение памяти программ микроконтроллеров STC89C51RC и STC89C52RC.

|  |

| Память программ STC89C51RC | Память программ STC89C52RC |

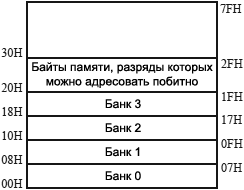

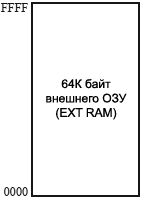

Data Memory. Это память, где могут размещаться только данные. Есть несколько разновидностей памяти данных.

On-chip Scratch-Pad RAM. Точно так же, как и у обычного микроконтроллера 8051, у MCU серии STC89xx имеется 256 сверхбыстрой памяти данных (SRAM), в которую входит пространство из 128 байт SFR. Младшие 128 памяти данных могут быть доступны как через прямую, так и через косвенную адресации. Старшие 128 байт памяти данных и 128 байт SFR используют общее адресное пространство. К этим старшим 128 байтам памяти данных можно получить доступ только с помощью косвенной адресации. К старшим 128 байтам SFR можно получить доступ только через прямую адресацию.

|

| On-chip Scratch-Pad RAM |

Младшие 32 байта (с адресами 00H..1FH) памяти данных сгруппированы в 4 банка по 8 регистров в каждом. Инструкции программы обращаются к этим 8 регистрам как к регистрам R0..R7. Биты RS0 и RS1 регистра PSW (см. секцию «Регистры SFR для доступа к RAM») выбирают, какой из этих банков сейчас используется. Инструкции, использующие регистровую адресацию, будут осуществлять доступ только к регистрам указанного в настоящий момент банка. Это позволяет более эффективно использовать пространство кода, поскольку инструкции с регистровой адресацией короче, чем инструкции, использующие прямую адресацию.

|

| Младшие 128 байт Internal SRAM |

Следующие 16 байт (20H..2FH) за банками регистров формируют блок области памяти, которую можно (с помощью специальных инструкций) адресовать как отдельные биты (флаги). Набор инструкций 80C51 включает в себя широкий набор инструкций для манипуляции одним битом, и 128 бит в этой области могут быть напрямую модифицированы этими инструкциями. Адреса бит в этой области могут быть в диапазоне 00H..7FH.

К младшим 128 байтам можно получить доступ либо прямой, либо косвенной адресацией, в то время как к старшим 128 байтам можно получить доступ только косвенной адресацией. Регистры специального назначения (SFR) включают защелки портов, регистры таймеров, управление периферийными устройствами и т. д. К этим регистрам можно получить доступ только прямой адресацией. 16 адресов в пространстве SFR могут быть адресованы и как байты, и как биты. SFR, которые могут быть адресованы как биты, имеют адреса, заканчивающиеся на 0H или 8H.

|

| Auxiliary RAM |

Для компилятора KEIL-C51 присваивание переменных, размещенных в Auxiliary RAM, должно использовать определение pdata или xdata. После компиляции переменные, декларированные через pdata и xdata, будут соответственно относиться к памяти, к которой осуществляется доступ через MOVX @Ri (для pdata) и MOVX @DPTR (для xdata). Таким способом можно корректно осуществлять аппаратный доступ к памяти MCU.

|

| External RAM |

[Регистры SFR для доступа к RAM]

Ниже показаны некоторые SFR, которые имеют отношение к RAM.

Для быстрого перемещения данных серия STC89xx поддерживает 2 указателя данных. Они используют общий адрес SFR, и могут переключаться битом DPS (AUXR1.0).

PSW. Это слово состояния выполнения программы, (Program Status Word, сокращенно PSW).

| Бит | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Имя | CY | AC | F0 | RS1 | RS0 | OV | F1 | P |

CY : Carry (флаг переполнения, или переноса).

AC : Auxilliary Carry Flag (флаг дополнительного переноса, применяется для BCD-операций; BCD расшифровывается как Binary Coded Decimal).

F0 : Flag 0 (доступен для пользователя как флаг общего назначения).

RS1 : Register bank select control bit 1 (бит 1 для выбора банка регистров).

RS0 : Register bank select control bit 0 (бит 0 для выбора банка регистров).

OV : Overflow (флаг переполнения).

F1 : Flag 1. Флаг, определяемый пользователем.

P : Parity (флаг четности аккумулятора).

Регистр AUXR.

| Бит | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Имя | — | — | — | — | — | — | EXTRAM | ALEOFF |

B7..B3: эти биты зарезервированы.

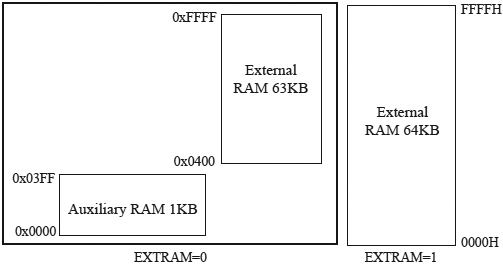

EXTRAM : переключает доступ к внутреннему/внешнему ОЗУ (Internal/External RAM access).

ALEOFF : запрет/разрешение генерации сигнала ALE.

0: ALE выдается с постоянной частотой, равной 1/3 от системной (SYSclk) в режиме 6T, и 1/6 от SYSclk в режиме 12T. 1: ALE активен только во время выполнения инструкции MOVX или MOVC.

Регистр AUXR1.

| Бит | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Имя | — | — | — | — | GF2 | — | — | DPS |

GF2 : флаг общего назначения, определяемый пользователем. Его может использовать программа приложения по любому назначению.

DPS : бит выбора регистров DPTR. Если 0, то выбран DPTR0 (по умолчанию); если 1, то для использования выбран вторичный DPTR (DPTR1).

Демонстрационный код для доступа к расширенной памяти см. в даташите STC89C51RC-en.pdf [2].

[Конфигурации GPIO]

MCU серии STC89xx имеет следующие ножки портов ввода/вывода (GPIO): P0.0..P0.7, P1.0..P1.7, P2.0..P2.7, P3.0..P3.7, P4.0..P4.3 (последние доступны только в корпусах LQFP44 и PLCC44). Все выводы портов могут быть независимо друг от друга сконфигурированы в одном из 4 режимов: quasi-bidirectional (квазидвунаправленный, стандартный порт выхода 8051), двухтактный выход (push-pull), только вход или выход с открытым стоком. По умолчанию (после сброса) все ножки портов находятся в режиме quasi-bidirectional. На каждом входе имеется триггер Шмитта для улучшения подавления помех.

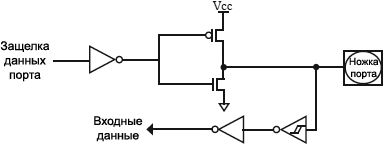

Quasi-bidirectional I/O. Ножки портов работают в quasi-bidirectional режиме выхода, как ножки портов стандартного 8051. Quasi-bidirectional можно использовать и как вход, и как выход, без необходимости переключения режима порта между входом и выходом. Это возможно, когда на выход ножки порта передан уровень лог. 1, тогда эта ножка имеет слабую подтяжку уровня к лог. 1 (weak pull-up), позволяя тем самым подключенным снаружи цепям подтягивать уровень к лог. 0 (так называемое монтажное ИЛИ с инверсией). Когда на выход ножки выводится лог. 0, то он может выдерживать большой ток (выход коммутируется открытым стоком порта MCU). Имеется на выбор 3 варианта pull-up для quasi-bidirectional порта, которые можно применять для разных целей.

Очень слабая подтяжка (very weak pull-up) подключается всякий раз, когда бит регистра порта содержит лог. 1. Эта очень слабая подтяжка выдает очень слабый ток, который достаточен для появления на ножке лог. 1, если она оставлена не подключенной к цепям, которые притягивали бы её к земле.

Второй вариант подтяжки, который называется просто слабой (weak pull-up), также включается, когда бит регистра порта содержит лог. 1, и ножка порта получает уровень лог. 1. Этот тип pull-up предоставляет основной источник тока для организации квази-двунаправленного выхода, который выводит лог. 1. Если этот вывод притягивается к лог. 0 внешним устройством, то этот weak pull-up выключается, и остается включенным только very weak pull-up. Чтобы перевести ножку порта в лог. 0 для этих условий, внешнее устройство должно быть способно проводить достаточный ток, чтобы понизить уровень на выходе, замыкая на землю ток от weak pull-up, и тем самым переводя уровень напряжения на выходе ниже его порога входного напряжения.

Третий вариант pull-up называется сильным (strong pull-up). Этот pull-up используется для ускорения переходов от лог. 0 к лог. 1 для квази-двунаправленной ножки порта, когда бит регистра порта меняет свое значение от лог. 0 к лог. 1. Когда это происходит, то strong pull-up включается на время 2 тактов CPU, быстро подтягивая уровень логики вывода к лог. 1.

Push-pull Output. Это режим работы порта как двухтактного выхода (push-pull), и структура работы порта какая же, как у открытого стока и квази-двунаправленного выхода с только тем отличием, что постоянно подключен strong pull-up, когда бит регистра порта содержит лог. 1. Режим push-pull может использоваться, когда для выхода требуется предоставить повышенный уровень тока. В этой конфигурации путь распространения входного сигнала для ножки порта такой же, как и quasi-bidirectional mode.

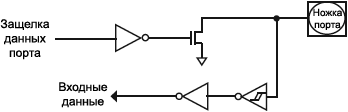

Input-only Mode. Это конфигурация, в которой ножка порта работает только как вход с триггером Шмитта, без какой-либо подтяжки на входе.

[Система команд]

Описание регистров специальных функций (SFR) и инструкций см. в главе 5 «Instruction System» даташита STC89C51RC-en.pdf [2].

[Прерывания]

Система прерываний MCU серии STC89xx совпадает с системой прерываний стандартного 8051. Описание системы прерываний, адресов векторов, уровней приоритетов, примеры кода см. в главе 6 «Interrupt» даташита STC89C51RC-en.pdf [2].

[Timer/Counter]

Описание таймеров/счетчиков, их регистров, режимов работы и примеры кода см. в главе 7 «Timer/Counter» даташита STC89C51RC-en.pdf [2].

[UART]

Описание улучшенного последовательного порта UART, его регистров, режимов работы и примеры кода см. в главе 8 «UART with enhanced function» даташита STC89C51RC-en.pdf [2].

[IAP/EEPROM]

Технология ISP в MCU серии STC89xx делает возможным обновление программы приложения пользователя в энергонезависимых данных приложения (находящихся в памяти IAP) без извлечения чипа MCU из конечного изделия (рабочей системы, где MCU работает). Эта полезная функция делает возможным обновление программ прямо на месте использования изделия (field-update). Обратите внимание, что для функции ISP необходимо, чтобы в память ISP была предварительно запрограммирована программа загрузчика (bootloader). Обычно от потребителя не требуется знать тонкостей принципа работы ISP, потому что компания STC предоставляет готовый, стандартный инструментарий ISP (управляющую утилиту программирования наподобие stc-isp-15xx-v6.85p.exe, см. архив [2]) и встроенный код ISP в памяти поставляемых образцов микроконтроллеров STC. Однако при самостоятельной разработке годного программного обеспечения для реализации функции ISP программист должен понимать архитектуру встроенной энергонезависимой памяти программ (embedded flash) и данных.

Embedded flash состоит из максимум 90 страниц. Каждая страница содержит 512 байт. Работая с flash, пользователь должен стереть (erase) страницу целиком перед тем, как он сможет записать (запрограммировать) данные на эту страницу.

Стирание памяти flash означает установку байт её содержимого в значение FFH. Для этого чипа доступно 2 режима стирания. Один режим это mass mode, и другой (page mode). Mass mode работает быстрее, но он очищает всю память flash целиком. Page mode медленнее, но зато он более гибкий, поскольку позволяет стирать память по одной странице. Работа в реальном времени с RAM отличается от работы с flash при очистке и записи тем, что для записи (программирования) flash требуется тратить время на ожидание завершения процесса.

Кроме того, для стирания/программирования flash требуется специальная довольно сложная процедура. К счастью, чипы серии STC89xx поставляются с удобным механизмом, помогающим пользователю читать/изменять содержимое flash. Просто заполните целевой адрес и нужные данные в несколько регистров SFR, и сработает встроенная автоматическая процедура ISP, так что пользователь может просто стирать, читать и программировать встроенную память flash и регистры опций.

Функция IAP (In-Application Program) разработана для того, чтобы пользователь мог читать/записывать энергонезависимые данные (nonvolatile data) памяти flash. Это может значительно помочь сохранять параметры приложения независимо от событий включения и выключения питания. Другими словами, пользователь может сохранять некие данные в памяти flash, и после этого выключить или перезагрузить MCU, и иметь возможность восстановить оригинальные значения данных, которые он сохранил ранее до выключения/перезагрузки.

Пользователь может программировать flash данных (data flash) таким же способом, как и программировать приложение в память flash по технологии ISP, но требуется более глубокое понимание назначения регистров SFR: ISP_DATA, ISP_ADDRL, ISP_ADDRH, ISP_CMD, ISP_TRIG и ISP_CONTR.

Регистры управления IAP/ISP. Ниже в таблице показаны регистры специальных функций (special function registers, SFR), относящихся к работе IAP/ISP. Все эти регистры могут быть доступны программно в приложении пользователя. Столбец POR/Reset показывает состояние регистра после включения питания / сброса.

| Символ | Описание регистра | Адрес | MSB | Адрес бита и символ | LSB | POR/Reset | |||||

| ISP_DATA | ISP/IAP Flash Data | E2h | 11111111b | ||||||||

| ISP_ADDRH | ISP/IAP Flash Address High | E3h | 00000000b | ||||||||

| ISP_ADDRL | ISP/IAP Flash Address Low | E4h | 00000000b | ||||||||

| ISP_CMD | ISP/IAP Flash Command | E5h | — | — | — | — | — | MS2 | MS1 | MS0 | xxxxx000b |

| ISP_TRIG | ISP/IAP Flash Command Trigger | E6h | xxxxxxxxb | ||||||||

| ISP_CONTR | ISP/IAP Control | E7h | ISPEN | SWBS | SWRST | — | — | WT2 | WT1 | WT0 | 000xx000b |

| PCON | Power Control | 87h | SMOD | SMOD0 | — | POF | GF1 | GF0 | PD | IDL | 00x10000b |

ISP_DATA: ISP/IAP Flash Data

| Бит | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Имя |

ISP_DATA это регистр порта данных для функционирования ISP/IAP. Данные ISP_DATA будут записаны по нужному адресу при операции записи ISP/IAP, и это также предоставляет доступ в окно данных при операции чтения ISP/IAP.

ISP_ADDRH: ISP/IAP Flash Address High

| Бит | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Имя |

ISP_ADDRH это порт для старшего байта адреса всех режимов ISP/IAP. Биты ISP_ADDRH[7:5] должны быть очищены (000b), и если хотя бы один из битов ISP_ADDRH[7:5] установлен, то операция записи IAP/ISP должна завершиться неудачно.

ISP_ADDRL: ISP/IAP Flash Address Low

| Бит | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Имя |

ISP_ADDRL это порт для младшего байта адреса всех режимов ISP/IAP. При операции очистки страницы (page erase) эта половина адреса игнорируется.

ISP_CMD: ISP/IAP Flash Command

| Бит | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Имя | — | — | — | — | — | MS2 | MS1 | MS0 |

Это регистр команд для управления операциями ISP/IAP. IAP_CMD используют для выбора режима flash при выполнении нескольких функций или используется для доступа к защищенным SFR.

B7..B3. Эти биты зарезервированы.

000: выключение (Standby).

001: чтение (Data Flash/EEPROM read).

010: программирование/запись (Data Flash/EEPROM program).

011: очистка страницы (Data Flash/EEPROM page erase).

ISP_TRIG: ISP/IAP Flash Command Trigger

| Бит | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Имя |

Регистр ISP_TRIG это порт команд для запуска активности ISP/IAP и доступа к защищенным SFR. Если ISP_TRIG заполнен следующими друг за другом байтами 46h, B9h, и если ISPEN (ISP_CONTR.7)=1, то сработает запуск активности ISP/IAP или доступ к защищенным SFR.

ISP_CONTR: ISP/IAP Control

| Бит | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Имя | ISPEN | SWBS | SWRST | — | — | WT2 | WT1 | WT0 |

Это регистр управления ISP/IAP.

0: общий запрет всего функционала ISP/IAP функций (program/erase/read).

1: разрешение функций program/erase/read для ISP/IAP.

0: загрузка из основной памяти после сброса.

1: загрузка из памяти ISP после сброса.

0: нет операции.

1: генерируется программный сброс системы. Этот бит будет автоматически очищен аппаратурой.

Примечание: действия программного сброса должны сбросить все другие SFR, но никогда не влияют на биты ISPEN и SWBS. Биты ISPEN и SWBS будут сброшены только сбросом при включении питания (power-up reset), но не программным сбросом.

B3. Этот бит зарезервирован. Программа должна записать в этот бит 0, когда записывается ISP_CONTR.

| Биты установки времени ожидания | Сколько ждет CPU в тактах системной частоты | Рекомендуемая системная частота, МГц | ||||

| WT2 | WT1 | WT0 | Чтение | Программирование, меньше 55 мкс | Стирание сектора, меньше 21 мс | |

| 0 | 1 | 1 | 6 | 30 | 5471 | 5 |

| 0 | 1 | 0 | 11 | 60 | 10942 | 10 |

| 0 | 0 | 1 | 22 | 120 | 21885 | 20 |

| 0 | 0 | 0 | 43 | 240 | 43769 | 40 |

Пример работы с IAP/EEPROM см. в даташите STC89C51RC-en.pdf [2].

[Таблица выбора микроконтроллеров STC89xx по размеру внутреннего EEPROM]